# 9. Transistors mosfets

Initiation à l'électronique

JEAN-MICHEL SALLESE

Initiation à l'électronique - Chapitre 9: Transistor MOS et logique CMOS - page 1

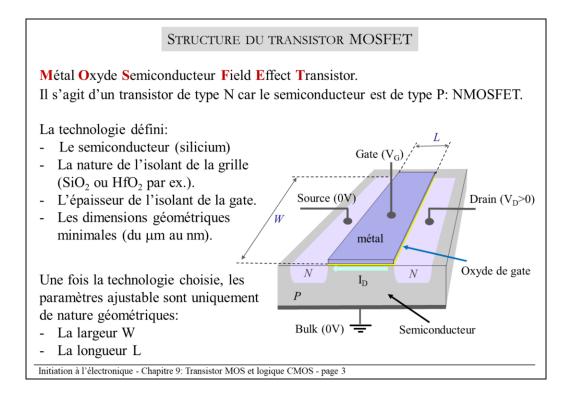

STRUCTURE DU MOSFET

LE MODÈLE ÉLECTRIQUE

Mosfet et Analogique: Exemple d'amplificateur

MOSFET ET NUMÉRIQUE : COMMUTATION ET LOGIQUE CMOS

Initiation à l'électronique - Chapitre 9: Transistor MOS et logique CMOS - page 2

Le transistor MOSFET est l'élément fondamental de la microélectronique et de la nanoélectronique contemporaine. Il s'est imposé dans les circuits depuis les années 1980, et n'a cessé d'évolué pour atteindre des dimensions de seulement quelques nanomètres.

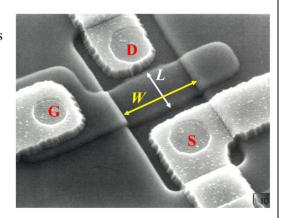

#### LE TRANSISTOR MOSFET - MICROPHOTOGRAPHIE

- Le MOSFET est l'élément actif plus utilisé dans les circuits intégrés.

Plus de 1 milliards de transistors

MOS dans un microprocesseur.

- La dimension typique d'un transistor MOS dans un microprocesseur est de quelques nanomètres seulement (le virus de la grippe est de l'ordre de 100 nm).

Initiation à l'électronique - Chapitre 9: Transistor MOS et logique CMOS - page 4

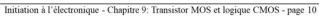

Vue au microscope électronique d'un transistor MOS avec grille en Silicium polycristallin. Les bandes claires sont les pistes d'aluminium qui réalisent les connexions entre les différents composants intégrés sur la puce.

La dimension caractéristique d'une technologie est donnée par la longueur minimale du canal sous la grille. Cette photo montre un transistor de technologie ancienne 1 µm.

Pour les technologies les plus récentes, on produit des transistors pour lesquel  $L_{\text{min}} \approx 7\,\text{nm},$  voire 5 nm.

Dans les microprocesseurs, la densité dépasse 1 milliard de ces transistors sur une surface de l'ordre du cm<sup>2</sup>.

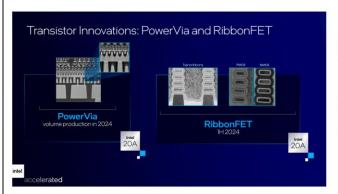

#### LE TRANSISTOR MOSFET - EVOLUTION

La course à la miniaturisation, connue sous le nom de loi de Moore, a conduit l'industrie des semiconducteurs à développer des solutions technologique sans précédent dans l'histoires des sciences et techniques.

https://www.theverge.com/2021/7/26/22594074/intel-acclerated-new-architecture-roadmap-naming-7nm-2025

Initiation à l'électronique - Chapitre 9: Transistor MOS et logique CMOS - page 5

Dans les technologies avancées de nanoélectronique, de nouvelles structure tridimensionnelles sont exploitées. Elles permettent de mieux contrôler les passage du courant et de limiter les pertes dues à des fuites de porteurs de charge.

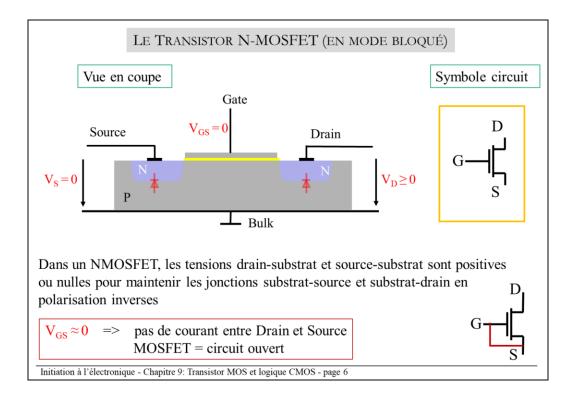

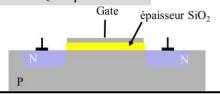

Le dopage du substrat est de type P.

Les contacts Source et Drain sont dopés de type N.

Il se créer donc une jonction pn entre ces contacts et le substrat.

En mode de fonctionnement normal, ces jonction sont polarisées en inverse et ne participent pas à la conduction.

Si aucune tension n'est appliquée sur le contact du gate, alors aucun courant ne passe entre la source et le drain.

Le transistor est bloqué, il se comporte comme un circuit ouvert.

Si la tension de la gate  $V_{GS}$  dépasse une certaine valeur, la tension de seuil  $V_{T}$ , des électrons sont attirés sous l'oxyde de la gate. Ils formeront un canal de conduction. Ce phénomène est appelé « l'inversion".

Ce canal a une résistance qui est alors commandée par la tension sur la gate.

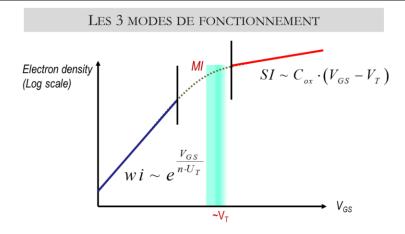

Selon la valeur de la tension de la grille  $V_{GS}$  vis-à-vis de la tension de seuil  $V_{T}$  on distingue 3 régimes de fonctionnement:

- Faible inversion (weak inversion)

- Inversion modérée (moderate inversion)

- Forte inversion (strong inversion)

Initiation à l'électronique - Chapitre 9: Transistor MOS et logique CMOS - page 8

Dans la suite, nous allons nous intéresser au régime particulier de la forte inversion, c'est-à-dire  $V_{GS} > V_T$

Dans ce mode de 'forte inversion, le transistor est plus rapide et il peut délivrer un courant important.

A l'opposé, le régime de la faible inversion est réserver aux applications à très faible consommation.

Entre les 2 régimes, il y a l'inversion modérée. Ce mode de fonctionnement est le plus complexe à modéliser, mais il a présente beaucoup d'avantages: faible consommation et rapidité.

Les équations qui décrivent le MOS sont assez complexes car elles dérivent de la physique des semiconducteurs. Cependant, on peut utiliser des relations simplifiées qui sont valables dans certains régimes de fonctionnement.

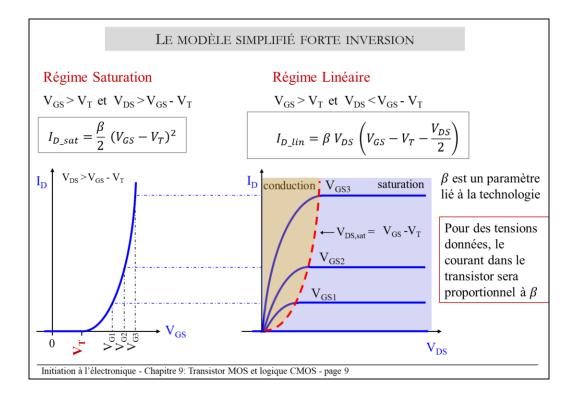

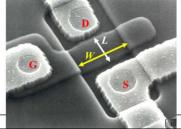

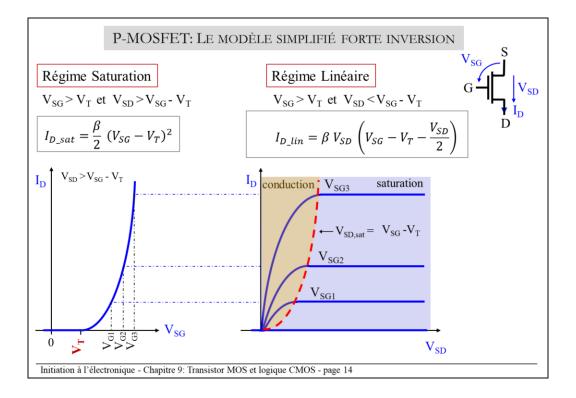

Ainsi, on distingue le régime de conduction, et le régime de saturation.

Ces modes de fonctionnement supposent que la tension  $V_{GS}$  dépasse la tension de seuil  $V_{T}$ . On appelle ce mode de fonctionnement la 'forte inversion'.

Si ce n'était pas le cas, i.e  $V_{GS} < V_{T}$ , alors supposera que le transistor est bloqué, c'est-à-dire qu'il ne laisse passer aucun courant.

En réalité ce n'est pas juste. Tout comme pour une diode polarisée en dessous de ' $U_J$ ', il existera bien un courant dans le canal qui variera de façon exponentielle avec  $V_{GS}$ , mais ce courant est très faible.

Des circuits analogiques à très faible consommation exploitent ce mode de fonctionnement que l'on appelle 'faible inversion'.

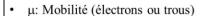

# Le paramètre technologique $\beta$

$$\beta = \mu C_{ox} \frac{W}{L}$$

$$\vec{V} = \mu \; \vec{E}$$

$\left( \overrightarrow{V}=1\ 10^{5}\ m/s \right)$  si 1 volt entre D et S distants de 1  $\mu m$

Capacité de l'oxide  $(\epsilon_0 = 8.86 \ 10^{-12} \ F/m^2)$

$$C_{ox} = \frac{\varepsilon_{ox}}{d}$$

$$\varepsilon = \epsilon_r \epsilon_0 = 3.9 \ \epsilon_0$$

$\varepsilon = \epsilon_r \epsilon_0 = 3.9 \ \epsilon_0$  Épaisseur Oxide SiO<sub>2</sub>: d=2nm  $C_{ox} = 0.017 \ F/m^2$

$$C_{ox} = 0.017 \, F/m^2$$

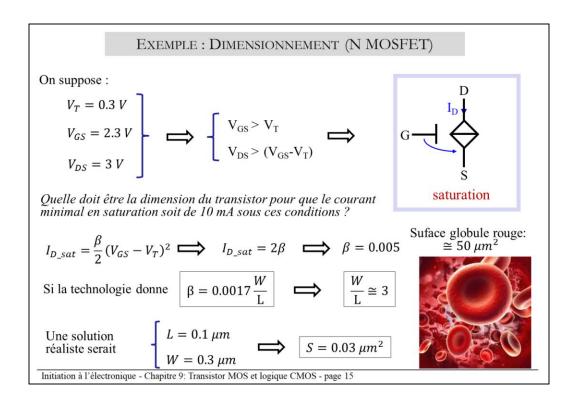

Pour une technologie donnée, le seul degré de liberté est le rapport W/L

$$\beta = \mu C_{ox} \frac{W}{L}$$

$$\beta = 0.0017 \frac{W}{L}$$

Remarque: la gate est isolée électriquement et son courant statique est toujours nul (en mode alternatif, il existe un courant de nature capacitif, mais il reste négligeable).

- Si  $V_{GS} < V_T$ , il n'y a pas de canal, donc le courant de drain est nul, le transistor est bloqué et se comporte comme un circuit ouvert.

- Si  $V_{GS} > V_T$ , il y a un canal de conduction entre source et drain.

Pour une faible différence de potentiel entre drain et source ce canal se comporte comme une résistance commandée par la grille.

Si V<sub>DS</sub> est voisin de zéro, le transistor est en conduction et se comporte comme une résistance commandée par la grille.

Lorsque la tension substrat-drain augmente, le canal tend à disparaître au niveau du drain.

Cette effet se traduit par un "pincement" du canal et une "saturation" du courant.

Cet effet se produit si  $V_{DS} \ge V_{Dsat} = V_{GS} - V_{T}$

Dans ce cas, le transistor est en saturation et se comporte comme une source de courant commandée par la grille, et non plus comme une résistance.

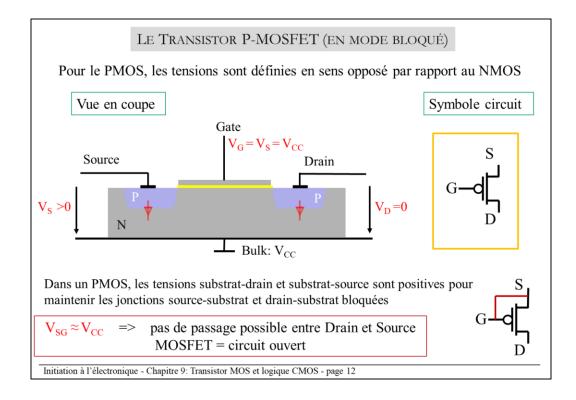

On peut intervertir les dopages du substrat et des zones Source et Drain.

Dans ce cas, on obtiendra un transistor de type P, P-MOSFET.

La conduction va s'effectuer au moyen de 'trous', l'équivalent des électrons mais avec une charge positive.

Ce changement de signe va se répercuter sur les tensions.

Aux signes près, les relations et les modes de fonctionnement d'un P-MOSFET et d'un N-MOSFET sont les mêmes.

Dans la pratique, et pour conserver les mêmes, dans le P-MOSFET es tensions sont définies dans le sens inverse par rapport au N-MOSFET.

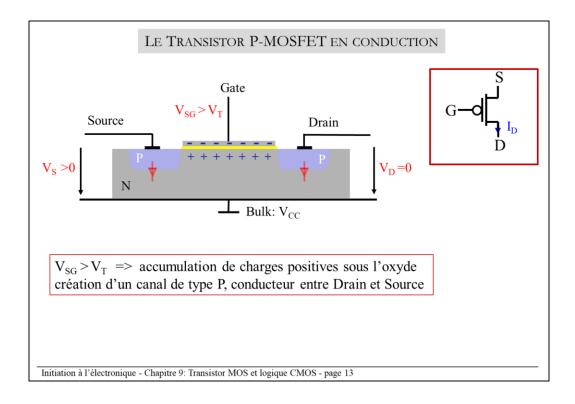

La tension substrat-grille positive attire des trous sous l'oxyde. Lorsque  $V_{SG}$  dépasse le seuil  $V_{T}$ , les 'trous' vont former un canal de conduction, un canal de type P.

Pour une faible différence de potentiel entre drain et source ce canal se comporte comme une résistance commandée par la grille.

Lorsque la tension substrat-drain augmente, le canal s'amincit du coté drain, le courant tend alors vers une constante, on dit qu'il y a "pincement" du canal et "saturation" du courant. Le transistor se comporte alors comme une source de courant commandée par la grille.

La grille est isolée et son courant est toujours nul.

- Si  $V_{SG}$  <  $V_{T}$ , il n'y a pas de canal, donc le courant de drain est nul, le transistor est bloqué et se comporte comme un circuit ouvert.

- Si  $V_{SG} > V_T$ , donc il y a un canal.

Comme pour le N-MOSFET, si  $V_{SD} < V_{Dsat} = V_{SG} - V_{T}$ , le transistor est en conduction et se comporte comme une résistance commandée par la grille.

Si  $V_{SD} \ge V_{Dsat} = V_{SG} - V_{T}$ , le transistor est en saturation et se comporte comme une source de courant commandée par la grille.

Connaissant la technologie, on peut dimensionner le transistor pour qu'il laisse passer un courant donné pour des tensions données.

Dans un circuit intégré on trouvera donc des transistors de différentes dimensions.

La dimension la plus petite que l'on peut implémenter dans le semiconducteur définit le 'nœud technologique'.

De nos jours, on parle de quelques nanomètres...

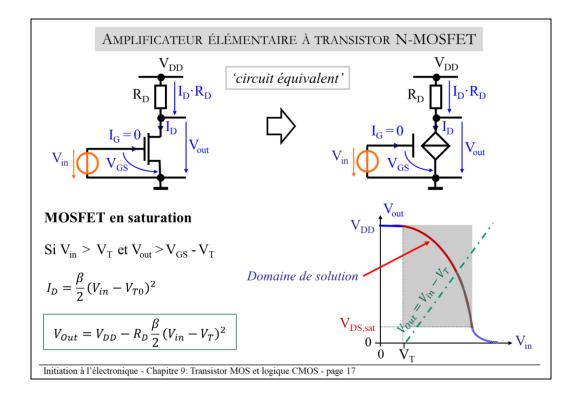

Pour réaliser des amplificateurs analogiques, on utilise des transistors MOSFET en saturation, c'est à dire comme des sources de courant commandées.

Le schéma ci-dessus représente l'amplificateur le plus simple que l'on puisse réaliser.

Par simplicité, on a choisi un N-MOSFET, mais bien entendu on pourrait réaliser la même fonction avec un P-MOSFET.

Dans les exemples qui vont suivre, nous avons choisi de polariser le transistor en forte inversion et en saturation, ceci pour des raisons également pédagogiques car les équations sont plus simples à résoudre.

Néanmoins, les autres modes de fonctionnement présente d'autres avantages dont nous ne parlerons pas ici.

# Condition sur R<sub>D</sub> pour être en saturation

$$V_{\text{out}} > V_{\text{in}} - V_{\text{T}}$$

et  $V_{\text{in}} > V_{\text{T}}$

$$V_{DD} - R_D \frac{\beta}{2} (V_{in} - V_T)^2 > (V_{in} - V_T)$$

$$R_D \le \frac{2}{\beta} \frac{V_{DD} - (V_{\text{in}} - V_T)}{(V_{in} - V_T)^2}$$

• Si on donne les conditions suivantes :

Sous ces conditions, si R<sub>D</sub> dépasse cette valeur, le MOSFET entrera en conduction

Initiation à l'électronique - Chapitre 9: Transistor MOS et logique CMOS - page 18

Pour s'assurer que le transistor opère en mode saturé, il faut établir dans ce cas précis une condition sur la résistance.

Si elle est trop élevée, la chute de tension à ses bornes sera importante et il ne 'restera' plus suffisamment de potentiel aux niveau du drain, ce qui polarisera le MOSFET en mode linéaire.

Dans l'idéal, un amplificateur doit délivrer un signal de sortie proportionnel à celui d'entrée.

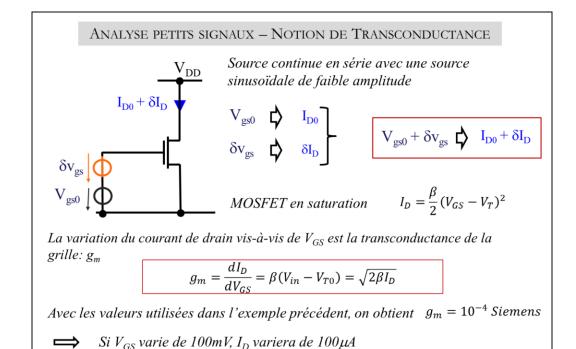

A cause de la non-linéarité de sa caractéristique I = f(V), l'amplificateur élémentaire à un seul transistor MOS ne peut s'approcher de ce modèle idéal que pour des petits signaux, superposés à une composante continue, appelée polarisation ou point de repos. Pour déterminer le gain d'un amplificateur, on analyse donc séparément la composante continue, que l'on calcule en utilisant le modèle non-linéaire du transistor, et la composante petit signal que l'on calcule en utilisant un modèle linéarisé du transistor.

C'est là qu'intervient la notion de transconductance g<sub>m</sub>.

Initiation à l'électronique - Chapitre 9: Transistor MOS et logique CMOS - page 19

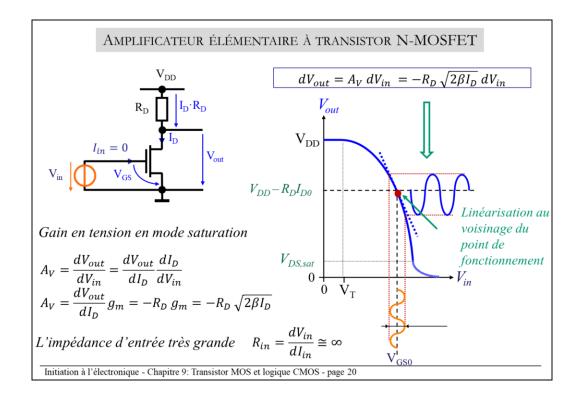

Un analyse simple montre que la variation de la tension  $V_{out}$  dépend à la fois de la transconductance  $g_m$  et de la résistance placée au drain  $R_D$ . (et bien entendu de  $V_{in}$ ).

Le lien entre  $V_{out}$  et  $V_{in}$  définit le gain  $A_V$  en tension du montage.

On voit que ce gain dépend également des paramètres géométriques du transistor  $(\beta)$  et du courant continu  $I_D$  utilisé pour le polariser.

Etant donné que la grille est une capacité, son impédance est infinie en tension continue.

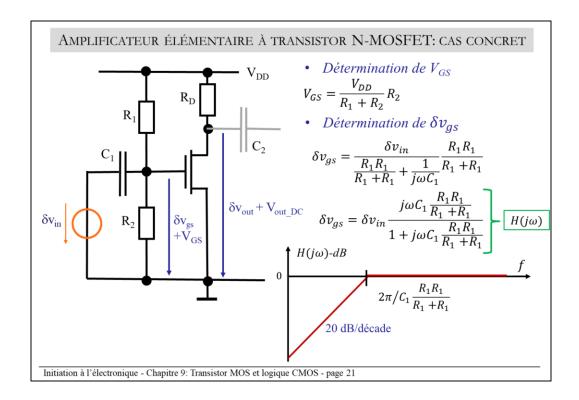

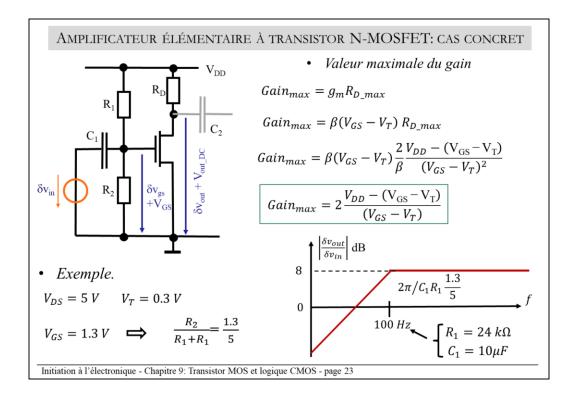

Dans les cas concrets, la polarisation continue est réalisée à partir d'un diviseur résistif, ici  $R_1$  et  $R_2$ .

Le signal à amplifié est appliqué à partir d'une connexion 'capacitive'.

En analysant ce montage, on déduite les valeurs continues de celles qui varient.

Ici, le choix de  $C_1$  et de  $R_1$  et  $R_2$  va également définir la bande passante à l'entrée.

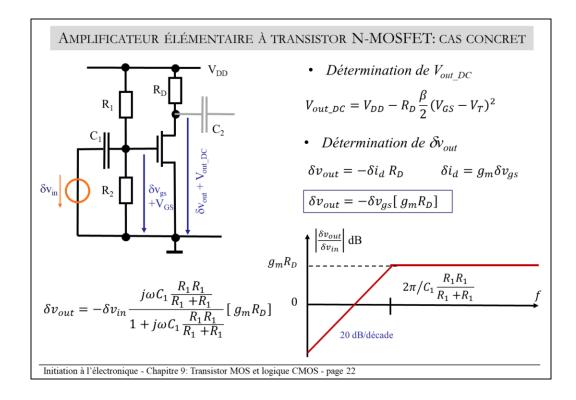

L'analyse de la tension de sortie fait apparaître les 2 contributions AC et DC. Pour l'instant, la capacité  $C_2$  est virtuelle, elle n'intervient pas dans nos calculs.

On peut en déduire le gain maximal de ce montage en utilisant la valeur maximale de la résistance  $R_D$  qui permet de satisfaire la condition de saturation du transistor. On remarque alors que ce gain maximal devient indépendant des paramètres technologiques du transistor, et qu'il ne dépend que de la polarisation (on suppose  $V_{GS} > V_T$ ).

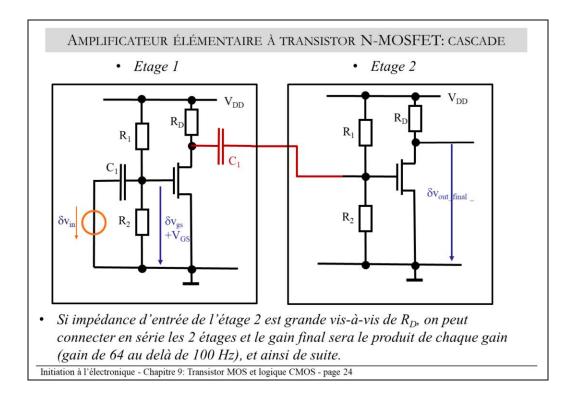

Pour augmenter ce gain, on peut utiliser cette tension de sortie amplifiée (AC) par l'étage 1 et l'appliquer à un circuit identique noté étage 2.

Si on suppose que l'impédance d'entrée de l'étage 2 est très grande vis-à-vis de l'impédance de sortie de l'étage 1, ici approximée à  $R_D$ , alors on peut effectuer le produit des gains pour obtenir le grain global de ce circuit.

Dans la pratique, les calculs sont plus complexes, ne serait-ce que parce que les signaux amplifiés finissent par ne plus être des 'petits signaux'.

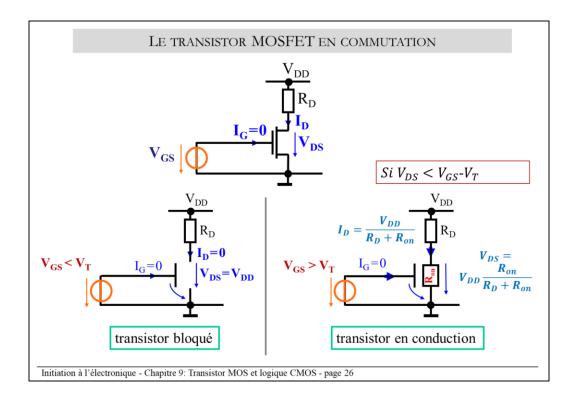

Le transistor MOS peut être utilisé comme un interrupteur drain-source commandé par la grille. C'est d'ailleurs cette fonction qui est largement exploitée dans les circuits numériques.

Ce type d'applications utilise les modes bloqué <=> circuit D-S ouvert, et conducteur <=> circuit D-S à faible résistance.

Ces deux modes de fonctionnement, blocage et conduction, sont utilisés pour faire des fonctions de logique binaire et de la commutation, pour enclencher/déclencher une charge  $R_{\rm D}$  par exemple.

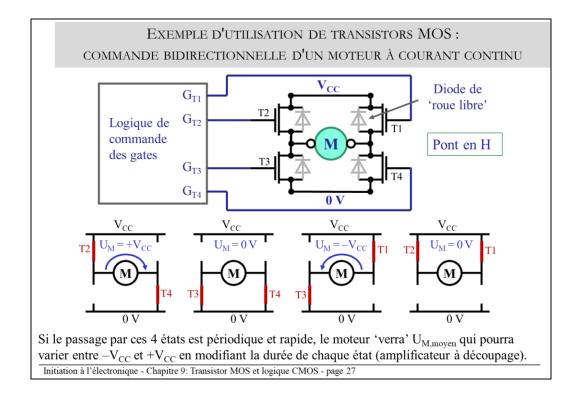

Dans cette application de commande d'un moteur, chacun des quatre transistors de puissance se comporte comme un interrupteur contrôlé par la grille grâce à un circuit de commande.

Plus la résistance de passage  $R_{on}$  des transistors est faible, plus les pertes sont réduites, ce qui permet d'obtenir des rendements > 90%.

En commutant les transistors à une fréquence supérieure à 1/(constante de temps électrique) du moteur, celui-ci n'est sensible qu'à la tension moyenne à ses bornes. Cette tension moyenne peut être commandée de  $-V_{\rm CC}$  à  $+V_{\rm CC}$  en variant la durée relative des différents états des transistors. C'est le principe des sources à découpage.

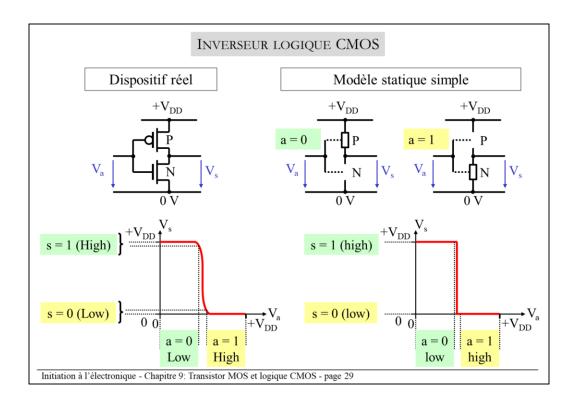

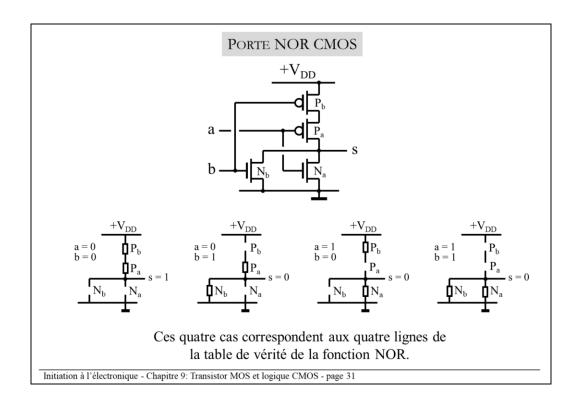

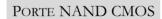

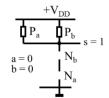

### LOGIQUE CMOS (COMPLEMENTARY MOS)

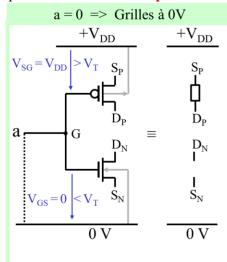

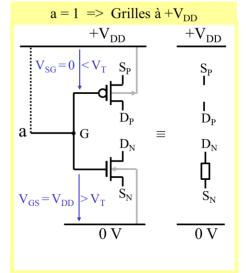

Toute variable logique d'entrée a commande les deux grilles reliées d'une paire de **transistors complémentaires**: un NMOS et un PMOS.

Initiation à l'électronique - Chapitre 9: Transistor MOS et logique CMOS - page 28

En logique CMOS le "0" logique équivaut à un potentiel quasi nul, le "1" logique équivaut à un potentiel égal à l'alimentation, habituellement noté  $V_{DD}$ . Lorsque l'entrée logique est à "0" le PMOS conduit et le NMOS est bloqué. Lorsque l'entrée logique est à "1" le NMOS conduit et le PMOS est bloqué.

Les différentes fonctions combinatoires sont obtenues en reliant les drains et sources des transistors associés à chaque variable logique.

La "porte " logique la plus simple est l'inverseur, réalisant la fonction de négation (NOT).

La caractéristique de transfert de l'inverseur réel a une zone de transition avec une pente élevée, ce qui a un effet discriminateur sur les niveaux logiques: un "0" (respectivement un "1") mal définit en entrée, dont la tension n'est pas véritablement proche de 0 V (respectivement  $V_{DD}$ ), sera un niveau "1" (respectivement "0") bien définit en sortie, proche de  $V_{DD}$  (respectivement de 0 V).

Dans un modèle simple, on considère une caractéristique de transfert idéale avec une transition verticale pour une tension d'entrée correspondant à la moitié de la tension d'alimentation.

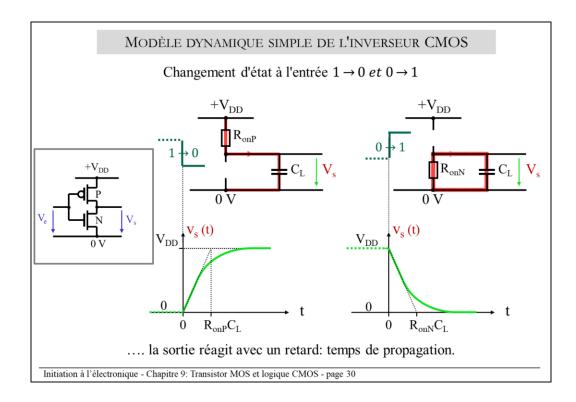

Toute connexion, et en particulier la sortie de l'inverseur, présente une capacité parasite contre la masse (somme des capacités parasites des drains des transistors de l'inverseur et des capacités des grilles des portes connectées à cette sortie).

A chaque transition de "0" à "1" de la sortie, cette capacité doit être chargée de  $0\,\mathrm{V}$  jusqu'à  $\mathrm{V}_{\mathrm{DD}}$  à travers le canal du PMOS. A chaque transition de "1" à "0" de la sortie, cette capacité doit être déchargée de  $\mathrm{V}_{\mathrm{DD}}$  jusqu'à  $0\,\mathrm{V}$  à travers le canal du NMOS.

Dans un modèle simple, on considère le canal comme une résistance.

Important: en logique CMOS, tant que les courants de fuite sont négligeables, il n'y a pas de courant statique, puisque les deux transistors complémentaires ne conduisent pas ensemble, que l'entrée soit à "1" ou à "0".

$$\begin{array}{c|c} & +V_{DD} \\ \hline P_a & P_b \\ a=1 & N_b \\ b=1 & N_a \end{array} s=0$$

Ces quatre cas correspondent aux quatre lignes de la table de vérité de la fonction NAND.

Initiation à l'électronique - Chapitre 9: Transistor MOS et logique CMOS - page 32